*Percobaan 1 Kondisi 4*

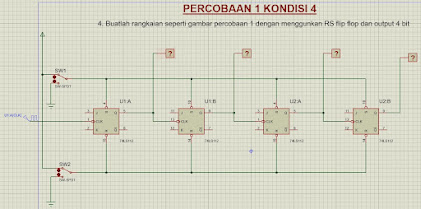

Buatlah rangkaian seperti gambar percobaan 1 dengan menggunkan RS flip flop dan output 4 bit

2. Gambar Rangkaian Simulasi

[Kembali]

3. Video Simulasi [Kembali]

4. Prinsip Kerja [Kembali]

Pada percobaan ini, flip flop yang digunakan bertipe R-S flip flop dimana kaki-kaki R dan S pada R-S flip flop tidak aktif atau dimasuki logika 1 (aktif low) yang diatur dengan switch SPDT. Output Q dari setiap R-S flip flop dihubungkan ke logic probe untuk mengetahui logika dari outputnya. Pada flip flop pertama, kaki clock dihubungkan dengan clock (sinyal pulsa). Selanjutnya, output Q dari flip flop pertama dihubungkan ke kaki clock pada flip flop kedua dan begitu seterusnya hingga flip flop keempat. Clock pada flip flop ini bersifat fall time (aktif ketika perubahan logika dari 1 ke 0).

Saat Clock pada flip flop pertama mengalami fall time, maka output Q1 pada flip flop pertama akan mengalami perubahan dari logika 0 ke 1. Output Q1 pada flip flop pertama ini mempengaruhi clock pada flip flop kedua dimana clocknya tidak aktif karena perubahan nilai dari 0 ke 1 sehingga ouput Q2 berlogika 0. Hal ini terjadi secara terus menerus hingga pada flip flop keempat. Pada percobaan ini, rangkaian asyncronus bertipe up karena menghasilkan bilangan decimal yang selalu meningkat

No comments:

Post a Comment